產品詳情介紹

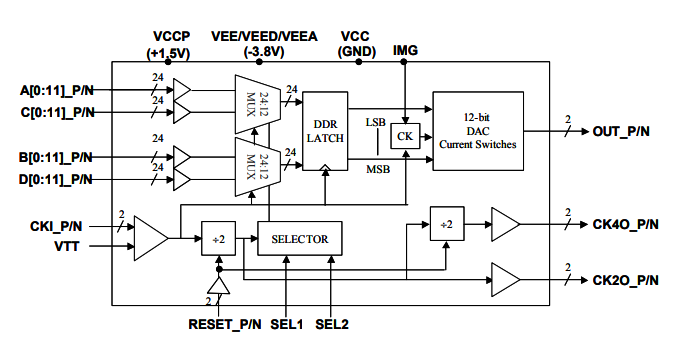

MD663B是一個高速12位數模轉換器(DAC),與每個DAC輸入位的4:1多路復用器集成。數字數據輸入是帶有片上100歐姆終端電阻的LVD。雙采樣率(DSR)DAC使其模擬輸出采樣率為時鐘速率的兩倍。該設備可以時鐘高達5ghz,以實現10gsps的DAC模擬輸出。互補模擬輸出可與50瓦輸出背面終端。用相位選擇(相位選擇)和相位選擇(相位選擇)劃分采樣和相位選擇。提供一個IMG引腳來調整時鐘驅動DAC的占空比,以最小化由于雙重采樣而產生的圖像信號。

主要特點

·DAC每個輸入位的4:1復用比率

·12位雙采樣率(DSR)DAC使模擬輸出采樣率為時鐘速率的兩倍

·時鐘頻率高達5GHz,DAC模擬輸出采樣率高達10GSPS

·超寬帶,帶寬從直流高達5千兆赫

·帶50瓦背面終端的互補輸出

·提供互補的除以2和除以4時鐘輸出用于數據同步

·時鐘驅動的DAC的占空比可以通過IMG管腳進行調整,以減少由于雙重采樣而產生的圖像信號

·可變400~800mvpp單端輸出擺幅

·每個差分輸入數據和復位對之間的芯片上100歐姆終端

·超低延遲:從數據采樣點開始計算3個時鐘周期或更少

·超低相位噪聲

·3.2 W功耗

·TQFP封裝,帶外露襯墊,增強散熱